How ESD Affects Electronics: ESD effects

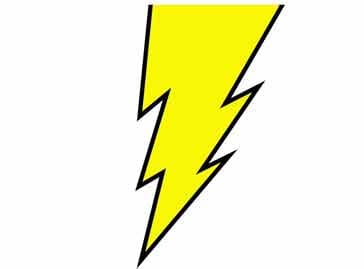

ESD, electrostatic discharge can affect electronic circuit and components in a variety of ways - some result in instant failure whereas others may appear weeks or years later.

Home » Construction & manufacture » this page

ESD Tutorial Includes:

ESD Basics

How ESD affects electronics components

Protecting against ESD

ESD protected area

ESD workbench

ESD work mat

ESD wrist strap

ESD clothing

ESD storage

ESD process

ESD on a budget

Design to combat ESD

ESD, electrostatic discharge affects electronic components in a number of different ways. The large static voltages can enter devices and cause damage to the intricate internal circuitry.

The effects of ESD have become more apparent as the high input impedances of MOS technology in all its forms have meant that voltages are not dissipated, and the small dimensions of both conductors and insulating barriers can easily be damaged by the very high voltages.

With integrated circuit feature sizes diminishing, this has meant that devices have become more susceptible to damage from static electricity.

ESD sensitivity

When looking at how ESD affects electronic devices, it is worth taking a look at the devices themselves and seeing how they are affected to ESD.

It is found that some electronic devices are more sensitive to ESD than others. However to put the problem in perspective it is worth relating the levels of static to those to supply voltages. One would not consider applying a voltage of even fifty volts to a logic device. Yet static voltages of several kilovolts can be applied to them by handling them without any ESD protective measures in place.

The devices that are most sensitive to ESD are generally those which include MOS - Metal Oxide Semiconductor technology. These devices have very high impedances which do not allow the charge to dissipate in a more controlled fashion. However this does not mean that bipolar devices are immune from damage.

Standard CMOS chips can be damaged by static voltages of as little as 250V. These include the 74HC and 74HCT logic families are widely used in many designs using "glue logic" because of their lower current consumption. However many of the new microprocessors and LSI chips use very much smaller feature sizes, and cannot withstand anything like these voltages, making them very sensitive to ESD. Many new devices would be destroyed by operating them with a supply voltage of 5 V, and they are corresponding more susceptible to damage from ESD.

Logic devices are not the only devices requiring anti static precautions to be taken. GaAsFETs which are used for RF applications are very susceptible to damage, and can be destroyed by static voltages as low as 100V. Other forms of discrete FETs are also affected by ESD. MOSFETs which are again often used for many RF applications are very sensitive.

Even ordinary bipolar transistors can be damaged by potentials of around 500V. This is particularly true of the newer transistors which are likely to have much smaller internal geometries to give higher operating frequencies. This is only a broad indication of a very few of the ESD susceptibility levels. However it indicates that all semiconductor devices should be treated as static sensitive devices, SSD.

It is not only semiconductor devices that are being treated as SSDs these days. In some areas even passive components are starting to be treated as static sensitive. With the trend to miniaturisation individual electronics components are becoming much smaller. This makes them more sensitive to the effects of damage from ESD.

Electrostatic discharge mechanisms

The effects of electrostatic discharge, ESD, are dependent on a large number of variables. Most of these are difficult to quantify. The level of static which is built up varies according to the materials involved, the humidity of the day, and even the size of the person has an effect. Each person represents a capacitor on which charge is held. The average person represents a capacitor of about 300 pF but this will vary greatly from one person to the next.

The way in which the discharge takes place also varies. Often the charge will be dissipated very quickly: typically in less than a hundred nanoseconds. During this time the peak current can rise to as much as twenty or thirty amps. The peak current and the time for the discharge are dependent upon a wide variety of factors. However if a metal object is used, like a pair of tweezers or thin nosed pliers the current peak is higher and reached in a shorter time than if the discharge takes place through a finger. This is because the metal provides a much lower resistance path for the discharge. However whatever the means of the discharge, the same amount of charge will be dissipated.

IEC61000-4-2 and other simulated waveforms

In order to combat ESD and to prevent damage resulting it is necessary to look at the different scenarios that may occur and to characterise them. These scenarios will exhibit different levels of voltage build up, different charge levels, and different discharge characteristics. Currently there are a number of methods for rating integrated circuits for ESD performance within the manufacturing environment. Three common methods include::

- HBM: Human Body Model - this model simulates a person becoming charged and then the discharge occurring via a bare finger through the circuit under test to ground.

- MM: Machine Model - this model simulates a charged manufacturing machine, discharging through the device to ground. The machine will have a conductive surface and therefore the resulting current levels can be much higher but for a shorter time.

- CDM: Charged Device Model - this simulates an integrated circuit becoming charged and then being discharged to a grounded metal surface. Gain short but high current levels may be experienced.

These methods work well for testing ICs within a manufacturing environment, but are not as applicable for system level applications. For this, electronics items including cell-phones, MP3 players, digital cameras and many more that have external connections need to be able to withstand electrostatic discharges.

The IEC61000-4-2 standard defines standard test conditions that electronic equipment should withstand. It assumes that the user will take no precautions to prevent any ESD damage, and it defines a variety of levels that the equipment should withstand.

The typical curve for an electrostatic discharge defined by IEC61000-4-2 has a rise time of about 1 ns and a peak current level of around 30A. The waveform is used as part of testing of the susceptibility of electronics equipment to electrostatic discharges.

Device Sensitivity Classification

The ESD Human Body Model and the Charged Device Model ESD test simulation methods include classification systems that define the component sensitivity to the specified model.

These ESD classifications provide easy grouping and comparing of components according to their ESD sensitivity The classification gives an approximate indication of the level of ESD protection that is required for the component.

| ESDS Component Sensitivity Classification - Human Body Model (ESD STM5.1-2007) |

|

|---|---|

| Class | Voltage Range |

| Class 0 | <250 volts |

| Class 1A | 250 volts to <500 volts |

| Class 1B | 500 volts to < 1,000 volts |

| Class 1C | 1000 volts to < 2,000 volts |

| Class 2 | 2000 volts to < 4,000 volts |

| Class 3A | 4000 volts to < 8000 volts |

| Class 3B | ≥ 8000 volts |

| ESDS Component Sensitivity Classification - Charged Device Model (ESD STM5.3.1-2009) |

|

|---|---|

| Class | Voltage Range |

| Class C1 | <125 volts |

| Class C2 | 125 volts to <250 volts |

| Class C3 | 250 volts to <500 volts |

| Class C4 | 500 volts to <1,000 volts |

| Class C5 | 1,000 volts to <1,500 volts |

| Class C6 | 1,500 volts to <2,000 volts |

| Class C7 | ≥ 2,000 volts |

ESD damage and failure mechanisms

The way in which ICs fail as a result of ESD also varies, and it is also dependent upon a number of factors including the way in which the charge is dissipated to the topology within the IC.

One of the most obvious way in which an IC can fail as a result of ESD occurs when the static charge represented as a very high voltage gives rise to a high peak current causing burn out. Even though the current passes for a very short time, the minute sizes within ICs can mean that the small interconnecting links wires or the devices in the chip itself can be fused by the amount of heat dissipated. In some instances the connection or component may not be completely destroyed. Instead it may only be partly destroyed. When this happens the device will continue to operate and may have no detectable reduction in its performance. At other times there may be a slight degradation in operation. This is particularly true of analogue devices where small fragments of material from the area of damage can spread over the surface of the chip. These may bridge or particularly bridge other components in the chip causing the performance to be altered or degraded.

Another way in which ESD can cause failure is when the voltage itself causes breakdown within the IC. It is quite possible for the voltage to breakdown an insulating oxide layer leaving the IC permanently damaged. Again this can destroy the chip immediately, or leave a partly damaged area with a latent failure.

Charge can also be transferred to electronic components in other ways and cause damage. It may result in damage either from voltage breakdown or by generating current to flow in the device. This may occur because a highly charged item will tend to induce an opposite charge in any article near it. Plastic drinks cups are very susceptible to carrying high static voltages and if they are placed on a work surface next to a sensitive piece of electronics they can induce a charge that may lead to damage. While good laboratory and workplace practice bans drinks from work areas, these cups should never even be used as receptacles for small bits such as screws, components, etc.

Latent ESD damage

When damage has been caused to the device, but it still remains operational, the defect leaves it with what is termed a latent defect. This form of ESD damage may lead to a failure later in its life. Subsequent current surges resulting from turning the equipment on, or even as a result of normal operation may stress the defect and cause it to fail. This may also be brought about by vibration in some cases.

These latent defects are of particular concern because this form of ESD damage may lead to failures later in the life of the equipment, thereby reducing its reliability. In fact manufacturing plants with poor anti-static protection are likely to produce low reliability equipment as a result of this. In fact it is estimated that for every device which suffers instant damage at least ten are affected by latent damage and will fail at a later date.

Another form of latent ESD damage occurs when large current pulses pass through metal-semiconductor contacts. The heating arising from this may be sufficient to cause local alloying of the aluminium and silicon. This may create what are termed alloy spikes that can propagate either horizontally or vertically from the contact pad. Eventually these may give rise to shorts with nearby junctions.

In addition to this it is found that the corners of diffusion wells within integrated circuits are very prone to latent ESD damage. This results from the field enhancement that occurs in these regions.

ESD Investigations

Although it is not easy to determine the cause of destruction of a device, some specialist laboratories have the means of making these investigations. They accomplish this by removing the top of the IC to reveal the silicon chip beneath. This is inspected using a microscope to reveal the area of damage.

These investigations are relatively costly. They are not normally undertaken for routine failures. Instead they are only undertaken when it is necessary to determine the exact cause of the failure.

ESD is a major concern for any company manufacturing electronic equipment. The damage caused by static discharges can cause a component to fail immediately and also it can cause latent failures to occur which can manifest themselves later, considerably reducing the overall reliability of the product.

More Construction Ideas & Concepts:

Soldering

SMT component soldering

ESD - Electro-Static Discharge

PCB manufacture

PCB assembly

Return to Constructional Techniques menu . . .